Industry Standard Physical Design Live Project. Of course some say synthesis should also be part of physical design but we will skip that for now.

Vlsi Soc Design Ir Drop Analysis Ii

3 Online Physical Design Training Institute with Placement.

. C Global route congestion. Industry standard Project Execution 1. Increases skew Use different power grid tap points for clock buffers but it makes routing more complicated for automated tools Use smaller buffers but it degrades edge ratesincreases delay Rearrange blocks More VDD pins Connect bottom.

IR drop occurs when there are cells with high current requirement or high switching regions. Vlsi pnr cts physicaldesign mtech cadence synopsys mentor placement floorplan routing signoff asic lec timing primetime ir electromigratio. This is for solving IR -drop issues.

If the value of IR drop is more than the acceptable value it calls to change the derate value. IR drop determines the level of voltage at the pins of standard cells. Power ring is designed around the core.

Electro Migration EM Current density checks on power network Depends on. D Physical information of the design. It occurs when the current density is high enough to cause the drift of metal ions in the direction of the electron flow and is characterized by the ion.

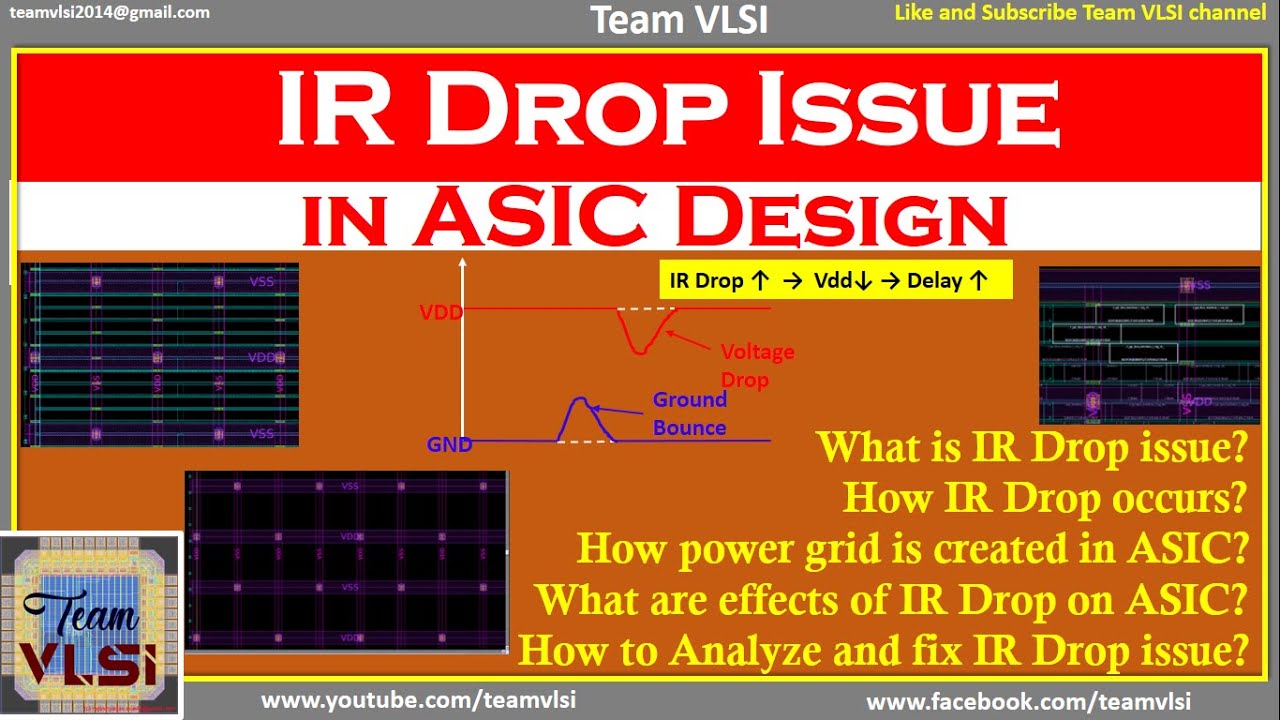

What are the different types of delay models. IR Drop is Signal IntegritySI effect caused by wire metal resistance and current drawn off from Power Vdd and Ground Vss grids. IR drop while causing an increase in delay for a digital transistor can have an even bigger impact on analog circuitry.

Given that the current draw of a wire is influenced by activity in other areas of the chip it is often seen as a source of noise for the analog circuitry and this has to be taken into account. IR Drop is Signal Integrity SI effect caused by wire resistance and current drawn off from Power Vdd and Ground Vss grids. B Allowable IR drop.

When voltage is applied to these metal wires power starts flowing through these metal layers. Value of acceptable IR drop will be decided at the start of the project and it is one of the factors used to determine the derate value. Power planning means to provide power to the every macros and standard cells and all others cells are present in the design.

Lecture 6 2 RAS Lecture 6 3 Clocked D Flip. Value of acceptable IR drop will be decided at the start of the project and it is one of the factors used to determine the derate value. Answer 1 of 3.

If the value of IR drop is more than the acceptable value it calls to change the derate value. IR drop determines the level of voltage at the pins of standard cells. High average current can cause for high Static IR Drop.

Normal buffinverters are having equal rise and fall times with high drive strengths compare to Clock buffinverters. Power planning is also called Pre-routing as the Power Network Synthesis PNS is done before actual signal routing and clock routing. IR drop is a voltage drop which affects technology node performance.

IR Drop and EM Analysis IR Drop Drop happens in supply voltage when traverses through the power network. Package cross-section showing IR drop components Combining 3 4 and the value for IR chip found in 2 provides a formula for determining an actionable IR drop target for the physical design process. IR Drop can be defined as the voltage drop in metal wires constituting power grids before it reaches the vdd pins of the cells.

Not only can timing change but it can directly cause functional failures. I am going to list out the stages from Netlist-GDS in this session. This is going to be a series of step-by-step explanation of physical design flow for the novice.

VLSI Physical Design MCQs. Flip-flop setup and hold times clock power clock latency skew jitter impact of IR drop on clock clock layout and routing clock synchronization. IR Drop analysis Static and Dynamic.

Mock Interviews Personality Improvement 1. If wire resistance is too high or the current passing through the metal layers is larger than the predicted an unacceptable Voltage drop may occur. Clock buffinverters are faster than normal buffinverters b.

IR Drop Analysis. Design current requirement Width of power meshes. What Is The Importance Of Ir Drop Analysis.

Similarly in dynamic analysis high transientswitching current can lead to high Dynamic. According to Ohms law V IR. IR core 775 mV IR package IR pads 5 To determine values for IRpackage and IRpads consider that IRpackage consists of two components.

Power requirement of the design Power network structure. IR Drop Analysis in Physical Design IR Analysis in VLSI. Clock buffinverters are having equal rise and fall times with high drive strengths compare to normal buffinverters d.

Design of the clock and the flops are related to each other so they should be studied together Design Issues. Well Tap Cells in Physical Design. Remedies Stagger the firing of buffers bad idea.

Static or Dynamic IR Drop is proportional to the current flowing through the power grid. Power rings contains both VDD and VSS rings. Clock buffinverters are slower than normal buffinverters c.

IR drop causes voltage drop which in-turn causes the delaying of the cells causing setup and hold violations. By using IR-A TA the impact of physical design changes that control or suppress the voltage drop or voltage variation could be quanti ed and the resulting. At that moment some voltage may get dropped due to the resistance of metal wires and power supply.

Electromigration is the gradual displacement of metal atoms in a semiconductor. I n this article we will discuss what is IR drop in ASIC design Why IR drop issue occurs what are the effects of IR drop and how t. A WLM wire load model b NLDM non linear delay.

Without this change timing calculation. The power supply in the chip is applied uniformly through metal layers.

Team Vlsi Ir Drop Analysis In Physical Design Ir Analysis In Vlsi

The Ir Drop Tolerant Pattern Generation Flow The Flow Utilizes The Download Scientific Diagram

Vlsi Soc Design Ir Drop Analysis Ii

Team Vlsi Ir Drop Analysis In Physical Design Ir Analysis In Vlsi

Ir Drop Issue In Vlsi What Is Ir Drop In Asic Why Ir Drop Effects Of Ir Drop Youtube

Team Vlsi Ir Drop Analysis In Physical Design Ir Analysis In Vlsi

Anasim Pi Fp Dynamic Voltage Droop Ir Drop Simulation And Spatiotemporal Power Integrity Aware Floorplanning

0 comments

Post a Comment